I can’t get the blinky project to work properly on the PIC32MZ CIP United board. I’ll explain here all the steps I’ve gone through in detail.

Note:

I’m working on UbuntuDescription: Ubuntu 23.04 Release: 23.04 Codename: lunar

1. Unzip the SDK, tools, and organize the files

As a first step, I unzipped the SDK I received from CIP United, as well as all the tools such as OpenOCD and the Mips toolchain they sent me. This is my folder structure now (scroll up and down in the grey area to see it all):

▼ ~/pic32

│

├─ env.sh

│

├─ ▼ sdk

│ │

│ ├─ ▶ build

│ ├─ ▶ docs

│ ├─ ▶ example

│ ├─ ▶ include

┆ ┆ ...

│ ├─ Makefile

│ └─ openocd.sh

│

└─ ▼ tools

│

├─ ▼ mips_toolchain

│ │

│ ├─ ▶ bin

│ ├─ ▶ Include

│ ├─ ▶ lib

┆ ┆ ...

│ └─ ▶ var

│

└─ ▼ openocd

│

├─ ▶ bin

└─ ▶ share

Note:

The'~/pic32/sdk'folder is basically the unzipped'PIC32MZ-Drivers'folder. I renamed that one into'sdk'because that felt cleaner to me.

2. Take care of environment variables

As you can see in the folder structure above, I added the file env.sh in the toplevel ~/pic32 folder. This file exports a few environment variables such that both the Mips toolchain and OpenOCD can be found. The file looks like this:

# Set environment variables for the CIP United board

# --------------------------------------------------

if [ "X$MSYSTEM" "==" "X" ]; then

if [ "X$name" "==" "Xenv.sh" ]; then

echo "Please source this file, rather than executing it."

exit

fi

env_name=$0

else

env_name=$1

fi

script=$(cd -P -- "$(dirname -- "$env_name")" && printf '%s\n' "$(pwd -P)/$(basename -- "$env_name")")

if [ "X$MSYSTEM" "==" "X" ]; then

export PIC_BASE=$(dirname "$script")

else

export PIC_BASE=$script

fi

echo $PIC_BASE

export OPENOCD_SCRIPTS=${PIC_BASE}/tools/openocd/share/openocd/scripts

export PATH=${PIC_BASE}/tools/openocd/bin:${PIC_BASE}/tools/mips_toolchain/bin:$PATH

I source this file each time I start working with the CIP United board.

3. Change openocd.sh

The sdk folder contains a openocd.sh file with the OpenOCD instructions to flash the board. These instructions seem to be for the WiFire board. So, I changed them. My '~/pic32/sdk/openocd.sh' file now looks like this:

#!/usr/bin/env bash

# OpenOCD flash command for WiFire board:

# openocd \

# -s ./openocd \

# -f ./openocd/wifire-pob.cfg \

# -f ./openocd/wifire.cfg \

# -c "init; halt"

# OpenOCD flash command for CIP United PIC32MZ board:

openocd \

-s ./openocd \

-f ./openocd/dp_busblaster.cfg \

-f ./openocd/pic32mz1024efg144.cfg \

-c "program {./build/uAptiv_Baremetal.elf} reset; shutdown;"

4. Let OpenOCD access USB drivers

To enable OpenOCD to access my Bus Blaster v3c probe, I went through the following three steps:

4.1 Add user to plugdev group

Add user to plugdev group:

$ sudo useradd -G plugdev `whoami`

4.2 Determine device’s Vendor ID and Product ID

I issue the following command to see which devices are connected to my laptop:

$ lsusb

Bus 004 Device 002: ID 0bda:0316 Realtek Semiconductor Corp. Card Reader

Bus 004 Device 001: ID 1d6b:0003 Linux Foundation 3.0 root hub

Bus 003 Device 006: ID 048d:ce00 Integrated Technology Express, Inc. ITE Device(8291)

Bus 003 Device 005: ID 048d:6005 Integrated Technology Express, Inc. ITE Device(8291)

Bus 003 Device 004: ID 04f2:b75c Chicony Electronics Co., Ltd FHD Webcam

Bus 003 Device 003: ID 046d:c52b Logitech, Inc. Unifying Receiver

Bus 003 Device 007: ID 8087:0026 Intel Corp. AX201 Bluetooth

Bus 003 Device 002: ID 0403:6010 Future Technology Devices International, Ltd FT2232C/D/H Dual UART/FIFO IC

Bus 003 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

Bus 002 Device 001: ID 1d6b:0003 Linux Foundation 3.0 root hub

Bus 001 Device 001: ID 1d6b:0002 Linux Foundation 2.0 root hub

The following line represents my Bus Blaster v3c probe:

Bus 003 Device 002: ID 0403:6010 Future Technology Devices International, Ltd FT2232C/D/H Dual UART/FIFO IC

That means:

- Vendor ID:

0403 - Product ID:

6010

4.3 Add device to plugdev group

I navigate to /etc/udev/rules.d in the terminal and list the contents there:

$ cd /etc/udev/rules.d

$ ls

70-snap.snapd-desktop-integration.rules

70-snap.snap-store.rules

70-snap.firefox.rules

70-snap.snapd.rules

I create a new file in this folder named 10-probe.rules and give it the following content:

ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6010", MODE="666", GROUP="plugdev"

I save the file and trigger Linux to reload the udev rules:

$ sudo udevadm trigger

Any member of the plugdev group should now be able to run OpenOCD and access the Bus Blaster v3c probe without using sudo.

5. Build GPIO project

Before I can flash the firmware, I need to build it first, obviously. This is what I did:

# Navigate into the toplevel folder:

$ cd ~/pic32

# Source the environment variables that give access to the tools:

$ source env.sh

# Navigate into the sdk folder:

$ cd sdk

# Clean and build the gpio project

$ make clean

$ make gpio BUILD=RELEASE

The firmware is now at ~/pic32/sdk/build/uAptiv_Baremetal.elf

6. Flash the firmware

To flash the firmware, I just need to run my openocd.sh script (see chapter 3 on how I modified that shell script). This is what I do:

# Navigate into the toplevel folder:

$ cd ~/pic32

# Source the environment variables that give access to the tools:

$ source env.sh

# Navigate into the sdk folder:

$ cd sdk

# Run the 'openocd.sh' script:

$ ./openocd.sh

Open On-Chip Debugger 0.12.0+dev-01279-gf0dd7c6 (2023-07-25-06:40)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : If you need SWD support, flash KT-Link buffer from https://github.com/bharrisau/busblaster

and use dp_busblaster_kt-link.cfg instead

Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'.

scan delay: 5000 nsec

running in fast queued mode

Warn : An adapter speed is not selected in the init scripts. OpenOCD will try to run the adapter at very low speed (100 kHz).

Warn : To remove this warnings and achieve reasonable communication speed with the target, set "adapter speed" or "jtag_rclk" in the init scripts.

Info : clock speed 100 kHz

Info : JTAG tap: pic32mz.cpu tap/device found: 0x17221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x1)

Warn : JTAG tap: pic32mz.cpu UNEXPECTED: 0x17221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x1)

Error: JTAG tap: pic32mz.cpu expected 1 of 1: 0x37221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x3)

Error: Trying to use configured scan chain anyway...

Warn : Bypassing JTAG setup events due to errors

Info : Reset Detected

Info : starting gdb server for pic32mz.cpu on 3333

Info : Listening on port 3333 for gdb connections

Info : JTAG tap: pic32mz.cpu tap/device found: 0x17221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x1)

Warn : JTAG tap: pic32mz.cpu UNEXPECTED: 0x17221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x1)

Error: JTAG tap: pic32mz.cpu expected 1 of 1: 0x37221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x3)

Error: Trying to use configured scan chain anyway...

Warn : Bypassing JTAG setup events due to errors

Info : Reset Detected

Info : Reset Detected

ISA implemented: MIPS32, microMIPS32

DSP implemented: yes, rev 2

FPU implemented: yes, disabled

FDC implemented: yes

PRID: 0x0001a720

CPU type: 0x004000b0, CP0 mask: 0x00000004

target halted in MIPS32 mode due to debug-request, pc: 0xbfc00000

** Programming Started **

Execution start_address = 0xa0070000

Info : device id = 0x17221053 (manuf 0x029 dev 0x7221, ver 0x01)

Info : flash size = 80kbytes

Info : device id = 0x17221053 (manuf 0x029 dev 0x7221, ver 0x01)

Info : flash size = 80kbytes

Info : device id = 0x17221053 (manuf 0x029 dev 0x7221, ver 0x01)

Info : flash size = 1024kbytes

Warn : no flash bank found for address 0x80000000

Warn : no flash bank found for address 0x80008200

Warn : no flash bank found for address 0xa0070000

** Programming Finished **

** Resetting Target **

Info : JTAG tap: pic32mz.cpu tap/device found: 0x17221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x1)

Warn : JTAG tap: pic32mz.cpu UNEXPECTED: 0x17221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x1)

Error: JTAG tap: pic32mz.cpu expected 1 of 1: 0x37221053 (mfg: 0x029 (Microchip Technology), part: 0x7221, ver: 0x3)

Error: Trying to use configured scan chain anyway...

Warn : Bypassing JTAG setup events due to errors

Info : Reset Detected

Info : Reset Detected

shutdown command invoked

Warn : Flash driver of pic32mz.flash0 does not support free_driver_priv()

Warn : Flash driver of pic32mz.flash0_upper does not support free_driver_priv()

Warn : Flash driver of pic32mz.flash1 does not support free_driver_priv()

7. Observe board behavior

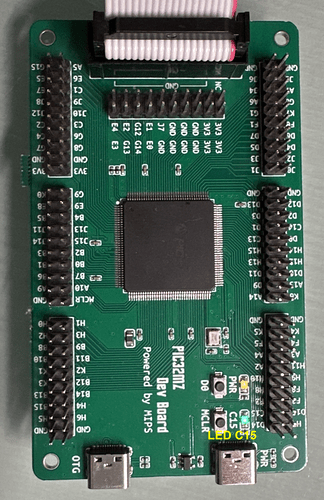

I took a picture of the board:

There is a green LED at the bottom with the label C15. It blinks, but always at the same speed. Even if I change the main.c file, I can’t get this LED to blink at another rate. This is the main.c file that I try to adapt:

~/pic32/sdk/example/gpio/gpio_led_on_off_polling/main.c

Its content:

#include "example/gpio/gpio_led_on_off_polling/peripheral/clk/clk.h"

#include "example/gpio/gpio_led_on_off_polling/peripheral/gpio/LED_gpio.h"

#include "include/pic32mz_clib.h"

#include "include/pic32mz_coretimer.h"

#define LED_On() LED_Set()

#define LED_Off() LED_Clear()

int main()

{

CLK_Init();

// No matter the number I insert here, the LED always blinks at the same speed.

CoreTimer_Initialize(1000, 0, 0);

CoreTimer_Start();

LED_GPIOInit();

LED_On();

while (1)

{

LED_Toggle();

// No matter the number I insert here, the LED always blinks at the same speed.

CoreTimer_DelayMs(1000);

}

}

What is going wrong?